by Kenneth A. Kuhn March 24, 2013

A log converter is a circuit that converts an input voltage to an output voltage that is a logarithmic function of the input voltage. Computing the logarithm of a signal is a very useful signal processing technique to compress a large dynamic range into a more manageable smaller range. Another application of log converters is performing complicated multiply, divide, and exponential functions. The inverse function, an exponential converter, is made by a modification to a log converter. An otherwise complicated mathematical function is facilitated by the natural exponential voltage to current function of a semiconductor junction. Accurate logarithmic conversion is possible over a range of four to over six decades of signal amplitude.

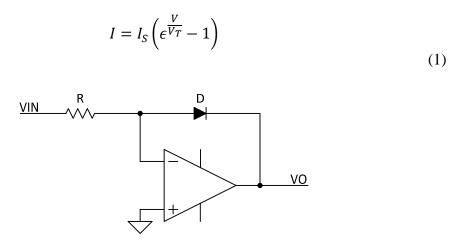

We start with the familiar diode equation but we will use a transistor junction instead as transistors are constructed to more exacting standards than diodes and exhibit more accurate log conformity over a wider dynamic range. Figure 1 shows the fundamental log converter circuit.

Figure 1: Simple log converter circuit

$V_{\rm O}$  is the negative of the forward diode voltage, V. The next step is to re-arrange Equation 1 as follows.

$$I + I_S = I_S \epsilon^{\frac{-V_O}{V_T}} \tag{2}$$

In real applications the junction current will typically be in the 100 nA to 1 mA range. The reverse saturation current, I<sub>S</sub>, is typically below 1 pA. So with small error we can modify Equation 2 as follows.

$$I = I_S \epsilon^{\frac{-V_O}{V_T}} \tag{3}$$

We next note that the diode current is  $V_{IN}$  divided by R. We substitute that into Equation 3.

$$\frac{V_{IN}}{R} = I_S \epsilon^{\frac{-V_O}{V_T}} \tag{4}$$

We now take the log of both sides of the equation with some re-arranging. Observe that in Equation 5 we appear to be taking the log of a current – which seems invalid as we can only compute the log of a dimensionless number. However, note that the  $I_S$  term originated in the denominator of the first log term which made that quantity a dimensionless current divided by current. Once the quantity is dimensionless we can factor out the numerator and denominator numbers (ignoring the apparent symbolic units) per the standard laws of logarithms as shown.

$$\frac{-V_O}{V_T} = \ln\left(\frac{V_{IN}}{RI_S}\right) = \ln\left(\frac{V_{IN}}{R}\right) - \ln(I_S)$$

(5)

Multiplying through by  $V_T$  gives us our final equation for the transfer function.

$$V_O = -V_T \left[ \ln \left( \frac{V_{IN}}{R} \right) - \ln(I_S) \right]$$

(6)

The circuit in Figure 1 thus produces an output voltage related to the log of the input voltage. However, there are two issues. One issue is that the thermal voltage,  $V_T$ , is a function of temperature. The other issue is that we generally do not accurately know the magnitude of  $I_S$  and it will also vary from component to component and is also a significant function of temperature. One remedy is to use a temperature regulator to hold the temperature of the diode constant. With temperature constant then the  $\ln(I_S)$  term is constant that can be removed by applying a compensating offset to the output. What we have so far is the basis for how a complete log converter circuit is built.

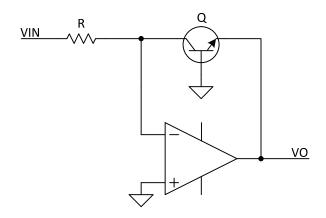

Figure 2 shows the preferred implementation of the circuit in Figure 1 using a transistor connected in what is known as a trans-diode. Both the collector and base are at zero volts and the diode junction is between the emitter and base. Unlike a typical diode which has a junction constant ranging from below 1.8 to above 2.2 and that varies with current, the junction constant of a transistor is 1.00 independent of current (at least over normal operating currents).

Figure 2: Log converter using the trans-diode connection

As an example of how this circuit operates, we will let R be a 10K resistor, we will use 100 fA for  $I_S$ , and 26 mV for the thermal voltage,  $V_T$ . We use Equation 5 to produce the following table. Observe that  $V_O$  changes by a very uniform 0.06 volts per decade of  $V_{IN}$ .

| VIN   | VO    |

|-------|-------|

| 10    | -0.60 |

| 1     | -0.54 |

| 0.1   | -0.48 |

| 0.01  | -0.42 |

| 0.001 | -0.36 |

Table 1: Basic log converter function

As simplistically shown, the circuit in Figure 2 will tend to have significant errors for input voltages below a few tens of millivolts. The dominant error terms are caused by the input offset voltage and bias current of the operational amplifier. For good results the operational amplifier should be a premium part with an input offset voltage well under 100 microvolts and an input bias current less than a few hundred picoamperes. The transistor can be a common 2N3904.

There are two other issues with the circuit in Figure 1. The gain of the transistor in the feedback of the amplifier can cause instability. If  $V_{\rm IN}$  goes evenly slightly negative the amplifier output will go upwards to the positive rail. The breakdown voltage of a reverse biased bas-emitter junction is only in the range from about five to seven volts. Thus, when the amplifier output voltage goes positive significant current is forced through the reverse biased base-emitter junction of the transistor resulting in damage or destruction. More advanced log converter circuits address the stability issue and protect the transistor.

#### More advanced circuits

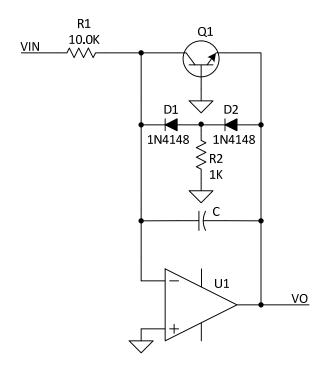

The first thing to do is add components to the circuit to address the feedback stability issue and possible damage to the transistor if  $V_{IN}$  is negative. Such a circuit is shown in Figure 3. The

input resistor,  $R_1$ , is 10.0K so that the full-scale input current from  $V_{IN}$  is no more than about a milliampere. For much higher currents there will be some errors to deal with.

Figure 3: Basic log circuit with feedback stability and transistor protection

The capacitor in the feedback slows the response of  $U_1$  so that it is stable. The required capacitance depends on the characteristics of  $U_1$  and generally has to be determined from experimentation. The goal is for the capacitance to be as small as possible consistent with stability over the full dynamic range of input. The capacitance will typically be in the range from several hundred picofarads to several nanofarads. As a result of the capacitor the response time of the circuit will become slower as  $V_{\rm IN}$  becomes smaller.

Diodes,  $D_1$  and  $D_2$ , and resistor,  $R_2$ , protect  $Q_1$  from excessive reverse voltage when the output of  $U_1$  goes positive in response to  $V_{IN}$  less than zero. The diodes will limit the maximum positive output voltage of  $U_1$  to around 1.2 volts which is safe for the transistor. In normal operation it is critically important that  $D_1$  not conduct any current that could be significant in comparison to the current through  $R_1$  when  $V_{IN}$  is small, say 1 mV. When  $V_{IN}$  is 1 mV the current through  $R_1$  and also  $Q_1$  is 100 nA. Under that condition the output voltage of  $U_1$  is approximately -0.36 volts. The data sheets for the 1N4148 diode specify a maximum reverse current of 25 nA with 20 volts reverse bias. With only 0.36 volts reverse bias the expected current would be significantly less – but there is no published data to reference. The primary path for that current is through  $R_2$ . If the current through  $D_2$  were as much as 25 nA then the voltage at the junction of  $R_2$  and  $D_2$  would be 25 microvolts. Since the cathode of  $D_1$  is at zero volts (virtual ground) then the reverse voltage across  $D_1$  is almost zero and any current through  $D_1$  will be very small – probably single digit nanoamperes or less. Thus, there is minimal interference to the normal operation of the log converter. It can sometimes be a challenge to incorporate protection circuitry that does not disturb normal operation.

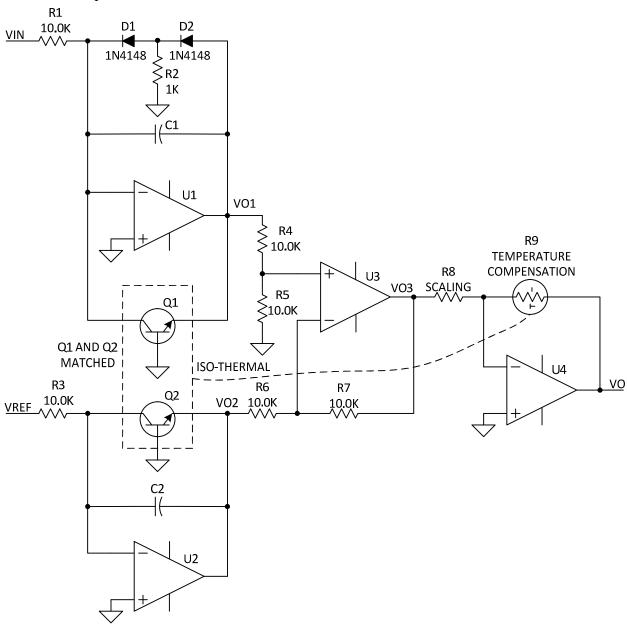

The next step is to assemble a more sophisticated circuit shown in Figure 4 that achieves stable performance with temperature and also has the ability to scale the output to a convenient factor such as 1 volt per decade.

Figure 4: Log converter with temperature compensation and scaling

The circuitry for processing  $V_{IN}$  is the same as in Figure 3. There is now a reference voltage input with similar processing to that of  $V_{IN}$  except that protection of  $Q_2$  is not needed since  $V_{REF}$  will be a fixed positive voltage which might range from one to ten volts. A concept critical to proper operation is that transistors,  $Q_1$  and  $Q_2$  (matched to have the same reverse saturation current), and a temperature compensating thermistor,  $R_9$ , are maintained at identical temperatures – typically by mounting them on an aluminum or copper structure. The absolute temperature

will vary with ambient but there will be no temperature gradient associated with these components. This concept enables temperature compensation to work.

Matching of the two transistors is achieved by purchasing them as part of a transistor array made on the same piece of silicon at identically the same time and identically the same process conditions. The matching will not be precisely perfect but it will be perfect enough. Unmatched discrete transistors could be used but there will some offset terms as a result of the mismatch. Those offsets could be adjusted out but are unlikely to track as well with temperature as a true matched pair.

The equations for  $V_{O1}$  and  $V_{O2}$  in Figure 4 are

$$V_{O1} = -V_T \left[ \ln \left( \frac{V_{IN}}{R} \right) - \ln(I_{S1}) \right]$$

(7)

$$V_{O2} = -V_T \left[ \ln \left( \frac{V_{REF}}{R} \right) - \ln(I_{S2}) \right]$$

(8)

V<sub>O3</sub> is V<sub>O1</sub> minus V<sub>O2</sub>

$$V_{O3} = -V_T \left[ \left( \ln \left( \frac{V_{IN}}{R} \right) - \ln(I_{S1}) \right) - \left( \ln \left( \frac{V_{REF}}{R} \right) - \ln(I_{S2}) \right) \right]$$

(9)

Simplifying Equation 9 gives

$$V_{O3} = -V_T \left[ \ln \left( \frac{V_{IN}}{V_{REF}} \right) - \ln(I_{S1}) + \ln(I_{S2}) \right]$$

(10)

If  $I_{S1} = I_{S2}$  as they would using matched transistors, then the output voltage of  $U_3$  becomes

$$V_{O3} = -V_T \left[ \ln \left( \frac{V_{IN}}{V_{REF}} \right) \right] \tag{11}$$

We now have a function that is independent on the reverse saturation current of the transistors but is still a function of temperature. VT is 0.0235 volts at 0C, 0.0257 volts at 25C and 0.0279 volts at 50C. We have a gain term that increases with temperature. The solution is to multiply by another gain term that decreases the same amount with temperature thus maintaining a constant net factor.

A thermistor is a temperature sensitive resistor with a negative temperature coefficient – the resistance decreases with an increase in temperature. It is intuitive to put such a device in the feedback of an inverting amplifier thus causing the gain to be inversely related to temperature as

shown with components,  $U_4$ ,  $R_8$ , and  $R_9$  in Figure 4. The thermistor must be thermally connected to the temperature of  $Q_1$  and  $Q_2$  as shown in the figure. Details are not shown but  $R_9$  is most likely a combination of a thermistor and perhaps one or two normal resistors in some series or parallel network to shape the gain as a function of temperature to compensate for the change in  $V_T$  with temperature over the temperature range of interest. The engineering for performing that is beyond the scope of this note.

The natural scale factor for silicon BJT log converters is around 0.06 volts per decade. We typically prefer a higher and definite factor of 1.00 or 2.00 volts per decade. Once the temperature compensation resistance of  $R_9$  is set we can adjust  $R_8$  for the desired scale factor. As an example, if  $V_{REF}$  is 10.00 volts and we desire an output scale factor of 2.00 volts per decade then  $R_8$  would be adjusted for an inverting gain of approximately (2/0.6) or 33. Then  $V_0$  would be per the following table.

| VIN    | <u>VO</u>                                                                     |

|--------|-------------------------------------------------------------------------------|

| 10     | 0.00                                                                          |

| 1      | -2.00                                                                         |

| 0.1    | -4.00                                                                         |

| 0.01   | -8.00                                                                         |

| 0.001  | -10.00 Attaining this level takes careful attention to detail and adjustments |

| 0.0001 | -12.00 Attaining this level takes extreme attention to detail and adjustments |

Table 2: Example 2 volt per decade log converter

An alternate concept to performing temperature compensation is to hold temperature sensitive components at a fixed temperature using an oven. Such could be done for the circuit in Figure 4 – holding the transistors at a temperature of perhaps 50C, maybe a little higher. Then the R<sub>9</sub> thermistor is not needed. Both concepts are used in practice. Temperature compensation is cheaper to implement and works fairly well although it is always an approximation. A temperature controlled oven costs more and is larger but provides absolutely stable performance. Which approach to take depends on what is important for the application.

### **Complete logarithmic converter**

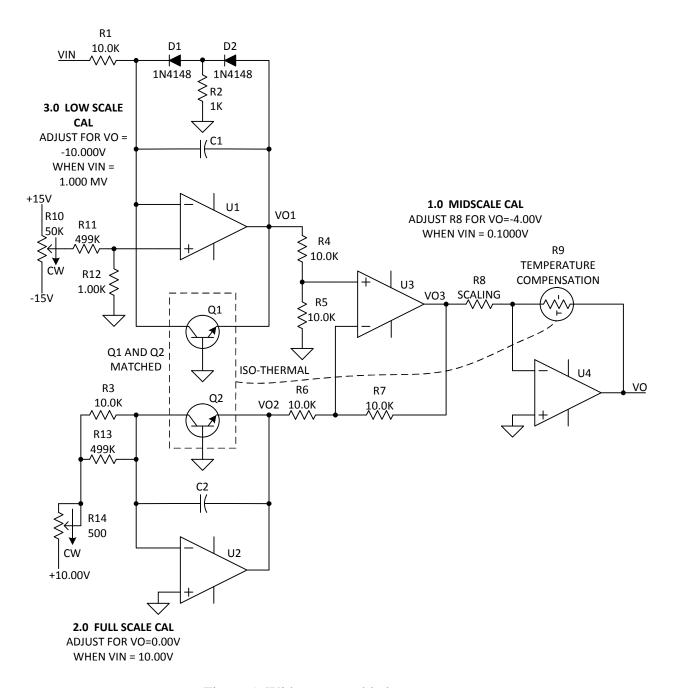

Figure 5 shows a complete logarithmic converter that is capable of wide dynamic range and is also temperature stable based on the basic circuit shown in Figure 4. Critical calibration adjustments have been added and the circuit is configured to produce the transfer function illustrated in Table 2. The circuit could alternatively be implemented with  $Q_1$  and  $Q_2$  in a controlled oven at say 50C and then  $R_9$  becomes just a simple resistor with no thermal connection. The circuit should be constructed with premium DC accurate amplifiers. Using conventional amplifiers such as the LM741 may limit the useful dynamic range to around three orders of magnitude. With premium parts it may be possible to approach a dynamic range of six orders of magnitude.

Figure 5: Wide range stable log converter

For accurate wide range results the collector of  $Q_1$  must be no more than a few tens of microvolts off of ground. The  $R_{10}$  adjustment compensates for any offset in  $U_1$  and enables this condition to be met.

Accurate calibration requires accurate input voltages of 10.00, 0.1000, and 0.001000 volts. The adjustment procedure is as follows.

- Step 1: MID-SCALE Calibration. Set  $V_{IN}$  to 0.1000 volts and adjust  $R_8$  for  $V_O = -4.00$  volts.

- Step 2: FULL-SCALE Calibration. Set  $V_{IN}$  to 10.00 volts and adjust  $R_{14}$  for  $V_{O} = 0.00$  volts.

- Step 3: Repeat steps 1 and 2 until no further improvement is attained.

- Step 4: LOW-SCALE Calibration. Set  $V_{IN}$  to 0.001000 volts and adjust  $R_{10}$  for  $V_O$  = -10.00 volts.

### Current input instead of voltage input

All of the examples shown in this note have pertained to an input voltage. The output signal for transducers such as photomultiplier tubes and photodiodes is a current rather than a voltage. The current signal from those can be converted to logarithmic form by these circuits if the input resistor is omitted and the transducer output is directly connected to the virtual ground of  $U_1$ . Interestingly, fewer errors result from the current input option and operation up to around seven decades of dynamic range is possible.

#### **Commercial log converters**

In general rather than building a log converter you can purchase an integrated circuit log converter from any of the major electronic integrated circuit companies such as Analog Devices and Texas Instruments and others. Check their web sites for product offerings, data sheets, and application notes – those provide much more information than contained in this note.